PIP PIP

Peripheral Component Interconnect Express (PCI Express or PCIe), as the name implies, is a type of board-level interconnect that allows high-speed data transfer between the processor chip (in our case, the BCM2712) and external peripherals (such as NVMe SSDs, Ethernet cards, or more exotic things like AI/ML accelerators).

Each lane of PCIe 2.0 (the fastest mode officially supported on Raspberry Pi 5) operates at a speed of 5Gbits/s; after accounting for encoding overhead, this translates to a capacity of 4Gbits/s. Even factoring in other protocol overheads, you might see speeds of up to 450MBytes/sec back and forth to a well-performing NVMe SSD. That's pretty fast!

In addition to data and clock channels, the PCIe specification also requires some sideband signals, such as reset, clock request (also serving as power state signals), and wake.

The Raspberry Pi's 16-lane connector provides all these signals. The Raspberry Pi also has two pins for controlling the board's power and ensuring that the Raspberry Pi firmware can automatically detect properly designed Raspberry Pi Peripheral (RPP) devices.

Not M.2

Why not add an M.2 interface to Raspberry Pi 5?

Because the M.2 interface is larger in size, relatively expensive, and requires a 3.3V 3A power supply. These factors together make it impractical to provide an M.2 interface within the standard Raspberry Pi form factor.

By using a small, low-cost FFC connector, we are able to provide a PCIe interface without enlarging the circuit board or imposing the cost of an M.2 connector and its accompanying power circuitry on every Raspberry Pi user.

The first specification

At the time of the Raspberry Pi 5 release, the official specifications for how to build peripherals that connect to the 16-lane PCIe interface were not yet ready. Detailed considerations were required for the interaction between PCIe peripherals and Raspberry Pi power states and firmware. The officials wanted to conduct extensive testing on their products to ensure everything operated as expected.

The first revision of this specification has been released by the Raspberry Pi Foundation.

URL:https://datasheets.raspberrypi.com/pcie/pcie-connector-standard.pdf

The second specification

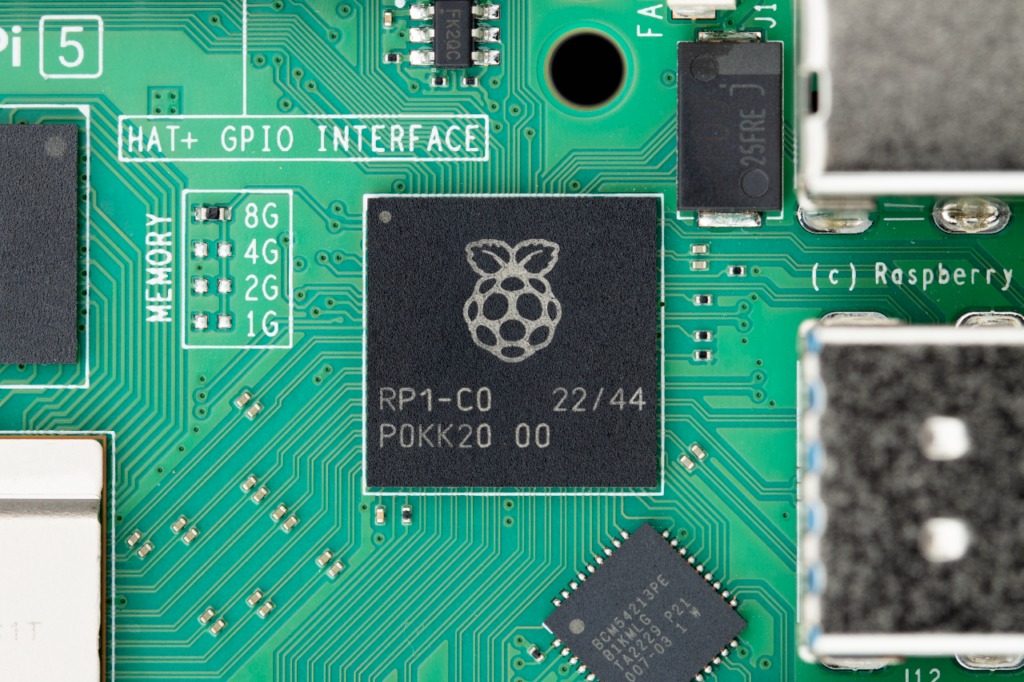

Astute readers will notice that the official term for the M.2 HAT is "HAT+." If you feel that one new specification isn't enough, the officials will also be releasing a preliminary version of the new HAT+ specification.

URL:https://datasheets.raspberrypi.com/hat/hat-plus-specification.pdf

The original HAT specification was written in 2014, so it's overdue for an update. Since then, there have been many changes. The new specification streamlines certain aspects, including the required EEPROM contents, and consolidates all the content into one document in the new Raspberry Pi documentation style, while also adding some new features.

There's still plenty of work to be done on the standard; the Raspberry Pi's EEPROM tools have yet to be updated to support generating the new-style EEPROM. Therefore, this release version is particularly suitable for users who want to understand the changes in the HAT standard.